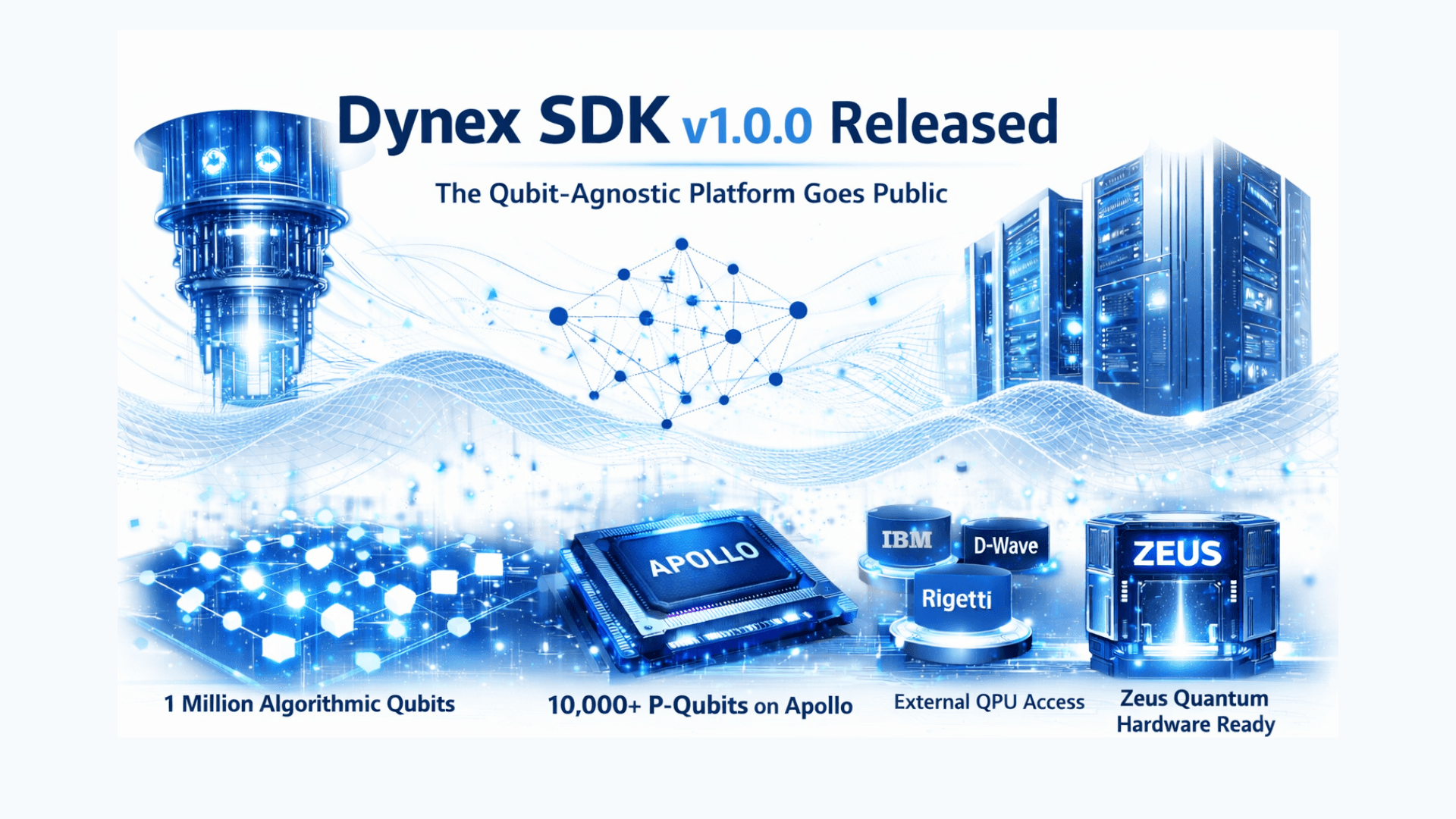

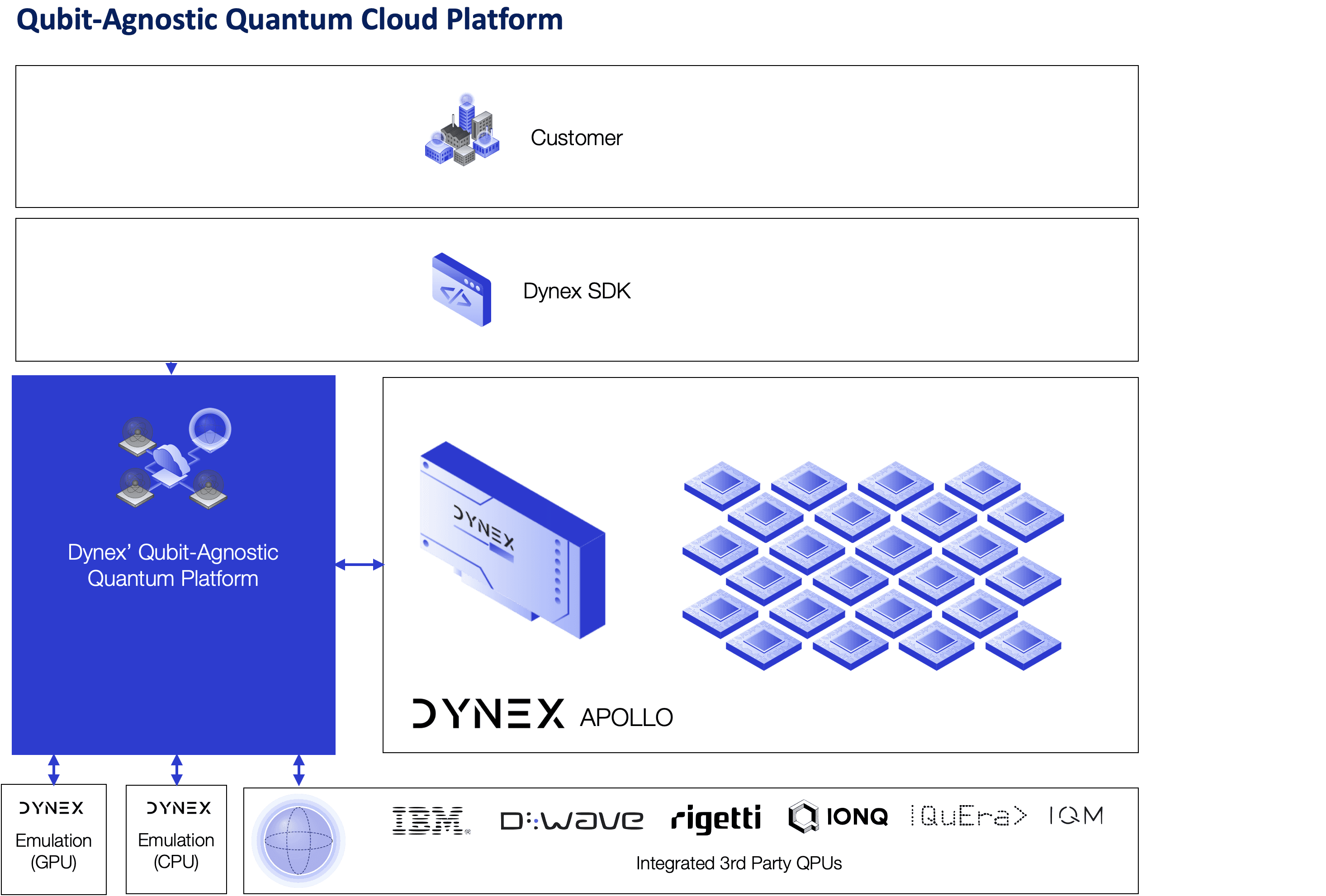

Dynex provides a qubit-agnostic computing platform designed to unify diverse quantum and quantum-driven compute resources under a single execution and programming environment. The platform enables users to access heterogeneous compute modalities through a consistent workflow for optimization, simulation, and probabilistic workloads—without requiring direct exposure to device-specific implementations.

The Dynex platform focuses on abstraction, orchestration, and interoperability, allowing end users to work at the problem level rather than the hardware level.

1. Platform Overview

1.1 Unified Execution Environment

Dynex presents all supported compute backends as standardized execution resources within a common runtime environment. These resources include:

proprietary Dynex compute systems,

large-scale software-based emulation resources, and

third-party quantum processing units operated by external providers.

A centralized orchestration layer manages workload submission, routing, execution coordination, and result handling. From the user’s perspective, workloads are expressed once and executed consistently, independent of the underlying compute modality.

1.2 Hybrid and Heterogeneous Workflows

The platform is architected to enable hybrid computational workflows, allowing multiple computing paradigms to be combined seamlessly within the lifecycle of a single problem. Rather than binding a workload to a fixed execution model, the system supports flexible orchestration across heterogeneous compute substrates. As a result, different stages of a computation—such as preprocessing, probabilistic sampling, optimization, or refinement—can be executed on the hardware or simulation environment best suited to the specific task.

Depending on availability, suitability, and performance requirements, workloads can be dynamically mapped to different backend resources, including classical high-performance systems, quantum emulation environments, neuromorphic probabilistic processors, or emerging room-temperature quantum hardware. Backend selection mechanisms evaluate factors such as the mathematical structure of the problem, the required computational precision, latency or throughput constraints, and the current availability of resources within the platform.

Importantly, this orchestration layer is designed to remain transparent to the application developer. Developers interact with the platform through a unified programming interface and abstract problem formulations (e.g., QUBO, Ising, or probabilistic graphical models), while the platform handles the underlying execution strategy. This abstraction allows users to focus on modeling and algorithm design, while the system automatically determines the most effective execution pathway across the available heterogeneous computing infrastructure.

2. Dynex Compute Systems

Dynex-operated compute systems are optimized for probabilistic and energy-based problem formulations commonly used in optimization, sampling, and inference. These systems are integrated into the Dynex platform as native execution resources and are accessed through the same APIs and tooling as other supported backends.

From a platform architecture perspective, these systems can be understood as specialized accelerators for probabilistic and combinatorial computation, designed to complement rather than replace existing classical and quantum hardware infrastructures. Instead of operating as isolated computing paradigms, they form part of a heterogeneous compute stack in which different physical substrates are leveraged according to their strengths in solving optimization, sampling, and stochastic inference problems.

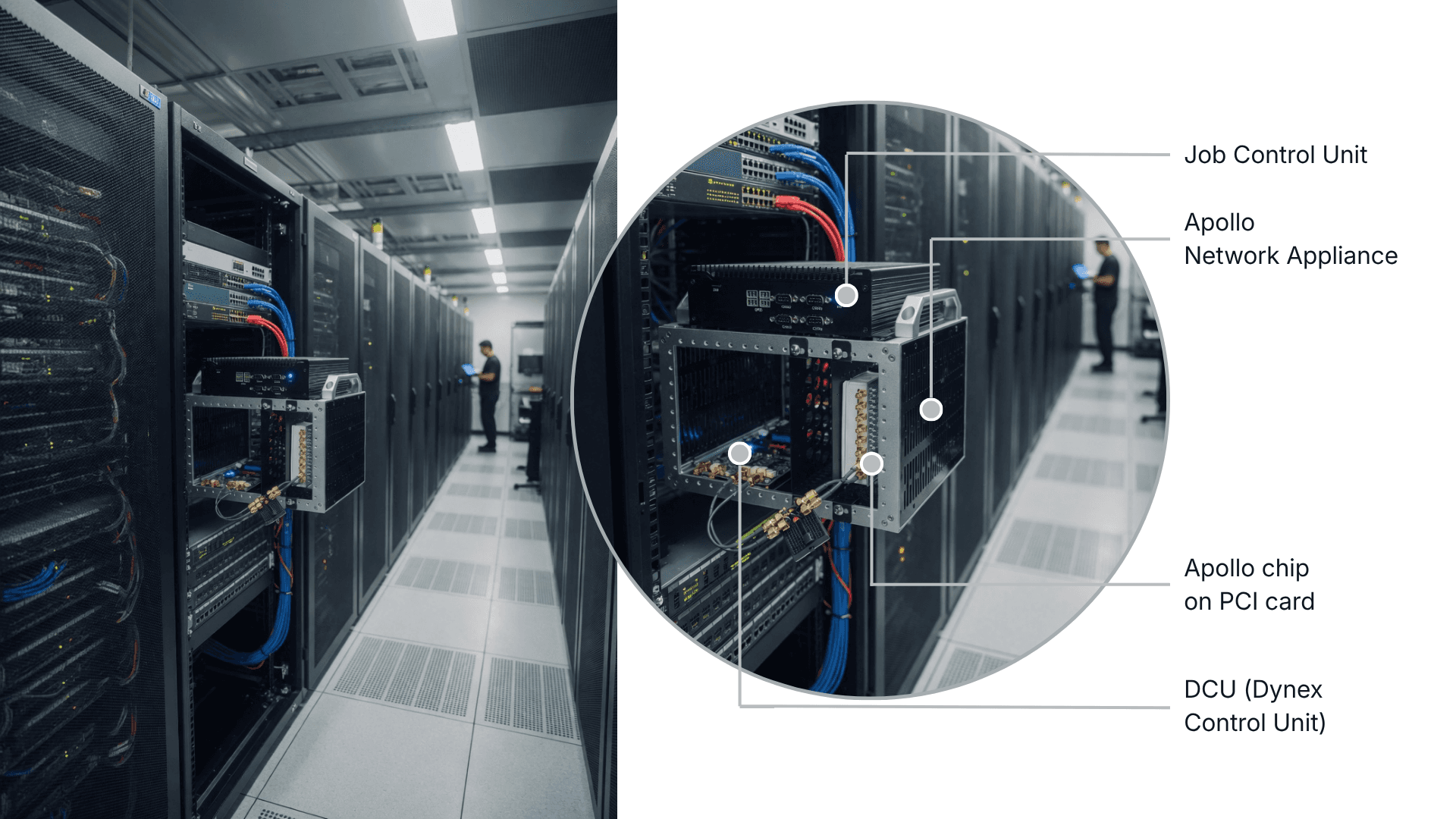

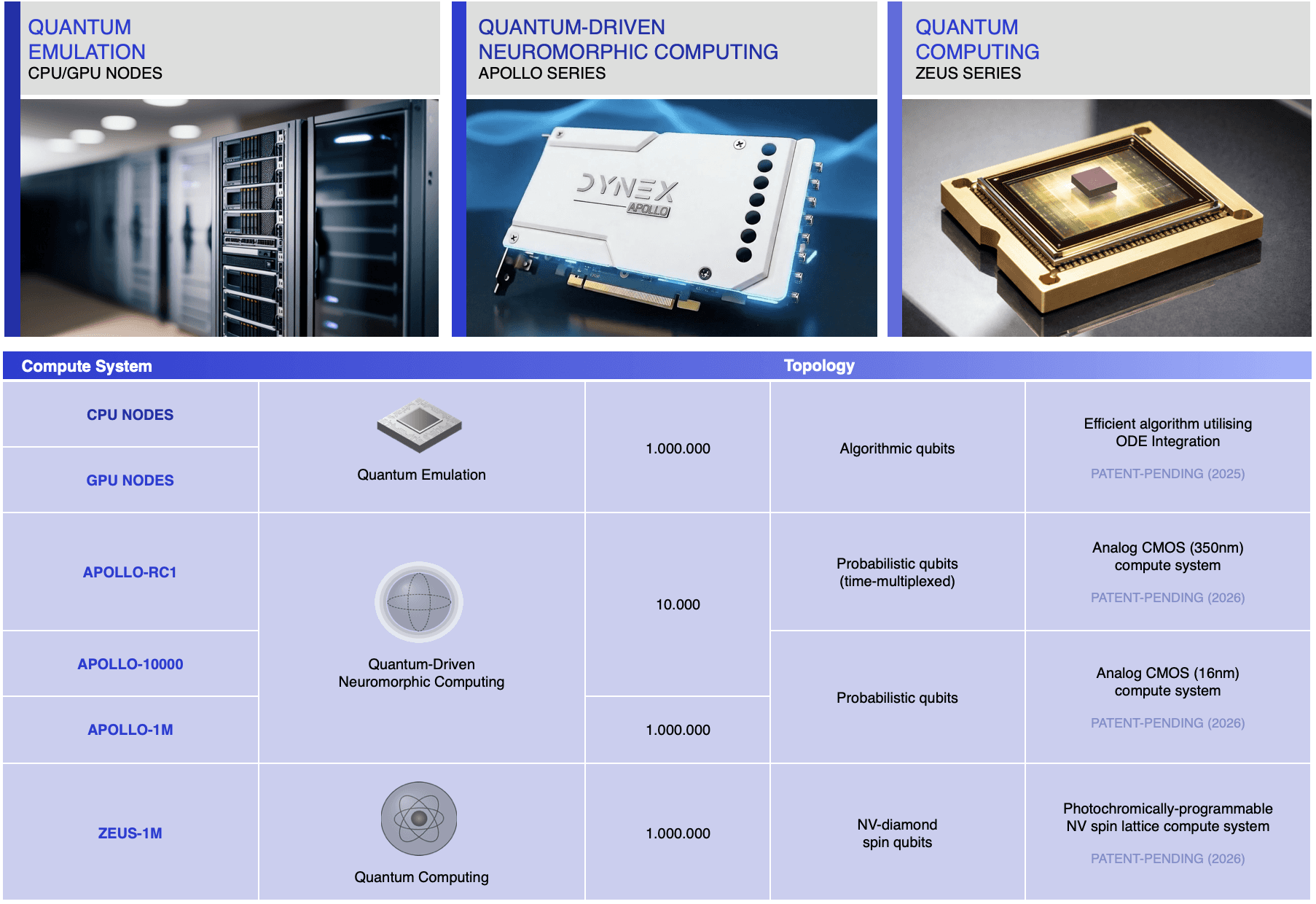

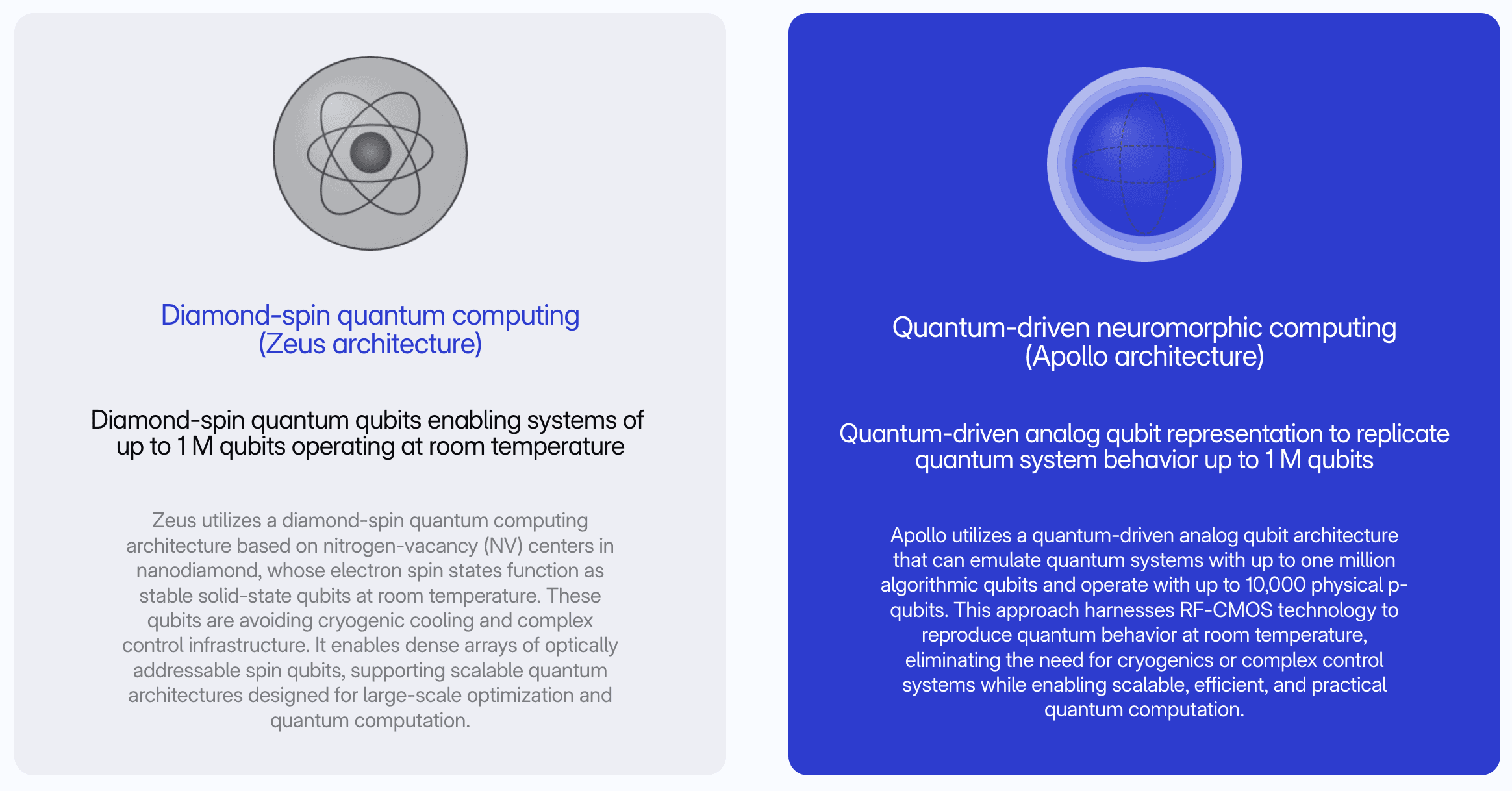

Within this framework, the available computational resources span several technological layers. At one end, high-performance quantum emulation systems implemented on CPU/GPU nodes enable the simulation of large-scale quantum circuits and quantum-inspired algorithms with substantial scalability. In parallel, quantum-driven neuromorphic computing systems based on analog CMOS technology (Apollo series) provide energy-efficient hardware substrates for probabilistic computing, enabling massively parallel exploration of energy landscapes typical of Ising and QUBO formulations. At the hardware frontier, a proprietary room-temperature quantum computing system built on nitrogen-vacancy (NV) diamond spin qubits (Zeus series) introduces a genuine quantum spin system that operates without cryogenic infrastructure, opening a pathway toward hybrid architectures where classical, neuromorphic, and quantum spin-based devices coexist within a unified computational ecosystem.

> Watch the Apollo video

> Academic paper: Quantum-Driven Neuromorphic Computing for Million-Qubit-Scale Workloads

> The Science Behind Dynex

3. Integration of External Quantum Hardware

Dynex supports interoperability with a range of external quantum computing providers across different hardware paradigms, including gate-based systems, annealing systems, and analog quantum simulators.

Provider | Device | Technology |

|---|---|---|

IBM | Eagle, others | Superconducting transmon (gate model) |

IonQ | Aria, Forte | Trapped-ion (gate model) |

Rigetti | Ankaa series | Superconducting (gate model) |

D-Wave | Advantage / Advantage2 | Quantum annealing |

QuEra | Aquila | Neutral-atom / Rydberg analog simulation |

IQM | Garnet, Emerald | Superconducting |

The platform abstracts differences in control interfaces, device topology, and execution semantics, enabling external quantum hardware to be used as complementary resources for experimentation, benchmarking, validation, or hybrid workflows.

4. Algorithmic Emulation Resources

In addition to physical hardware, Dynex provides access to high-performance software-based emulation resources designed to support large problem instances, development workflows, and reproducible experimentation.

These resources integrate seamlessly with the same SDK and runtime environment, allowing users to develop, test, and validate workloads before or alongside execution on specialized hardware.

up to 1 million algorithmic qubits,

deterministic reproducibility,

flexible embedding,

and compatibility with the same SDK used for Apollo and QPUs.

GPU qNodes are particularly suited for:

large-scale sweeps,

embedding validation,

debugging of Hamiltonian structures,

and scenarios where massive problem sizes exceed practical physical qubit counts.

> Benchmarks

> Academic paper: Benchmarking the Dynex Quantum Platform: A Comparative Evaluation of Quantum Algorithm Performance and Scaling

> The Science Behind Dynex

5. SDK and Programming Model

The Dynex SDK provides a unified programming interface for expressing optimization, probabilistic, and quantum-inspired workloads. Users interact with the platform through high-level representations such as:

optimization problem formulations,

probabilistic models,

graph-based structures, and

circuit-derived abstractions.

The SDK handles compilation, transformation, and backend adaptation internally, enabling portability across supported execution resources.

> Dynex SDK

> Dynex SDK Documentation

6. Runtime and Deployment Model

6.1 Managed Execution

The Dynex runtime environment is designed for flexible, managed execution. Compute resources may be provisioned dynamically, workloads may be rerouted as needed, and results may be returned incrementally or upon completion, depending on workload characteristics.

6.2 Distributed and Federated Operation

Compute resources supported by Dynex may operate in Dynex-managed environments, partner facilities, or distributed deployments. The platform coordinates execution across these environments while maintaining a unified user experience.

7. Application Areas

The Dynex platform supports a wide range of application domains, including but not limited to:

Optimization

combinatorial optimization

scheduling and routing

portfolio and risk modeling

constraint satisfaction problems

Sampling and Inference

probabilistic sampling

Bayesian inference

statistical and stochastic modeling

Hybrid Quantum Workflows

circuit-inspired problem representations

benchmarking and verification across hardware types

exploratory hybrid execution strategies

Machine Learning Acceleration

energy-efficient inference

probabilistic modeling

hybrid analog-digital workflows

> Industries

> Examples

> Use-Cases

8. Technical Documentation

Detailed technical specifications and hardware-level documentation for Dynex-operated compute systems are provided separately under controlled disclosure.

Note: Technical descriptions are intentionally non-exhaustive and do not disclose implementation details.